LE SYSTÈME INFORMATIQUE EMBARQUÉ

(N.D.R.) Sur cette page nous ne traiterons seulement que de l'AGC Block II, le seul ayant volé d'Apollo 7 à 17.

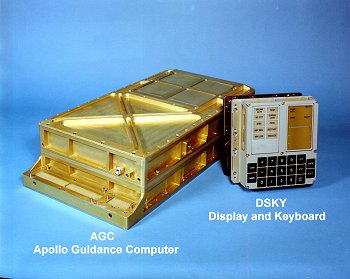

Le système informatique embarqué (1) du module de commande (CSS, Computer Subsystem) se compose de deux dispositifs complémentaires :

- L'ensemble DSKY (pour Display and Keyboard, affichage et clavier) et AGC (Apollo Guidance Computer ou encore CMC : Command Module Computer pour ordinateur de guidage d'Apollo) pour la partie matériel (hardware) et la partie logiciel (software).

SOMMAIRE :

Le DSKY

L'AGC

Le Software de l'AGC

PARTIE HARDWARE

En substance, le DSKY est un simple terminal de l'AGC. Il utilise des relais électromécaniques pour commuter les segments d’un écran luminescent alimenté en 250 V alternatif à 800 Hz, ainsi que des transistors pour la logique associée. Ces relais pilotent l’affichage des informations, bien que leur fonctionnement puisse introduire un certain délai dans la mise à jour visuelle. |

Le DSKY du Block II (Display and Keyboard, abréviation DSKY prononcé "disky" ou encore DISS-kee, pour unité d'affichage et clavier) est l'interface utilisée par les astronautes pour communiquer avec l'unité centrale de l'ordinateur du vaisseau Apollo. Les astronautes tapent les chiffres relatifs aux actions qu’ils souhaitent entreprendre et au programme qu’ils souhaitent modifier. Cette interaction "prend la forme d'une conversation grammaticale", assez facile à utiliser pour les personnes des années 60 qui n'ont jamais vu et utilisé un ordinateur auparavant.

Il permet à l'opérateur de charger des informations dans l'ordinateur, de demander des informations, de lancer divers programmes stockés en mémoire et d'effectuer des tests sur l'ordinateur et d'autres sous-systèmes du système PGNCS. Le DSKY fournit également une indication sur les changements d'état et d’avertissement susceptibles de se produire au sein de l’AGC. Il facilite donc seulement le moyen d'entrer des données au clavier dans le CMC, et d'en afficher les paramètres ainsi obtenus après traitement de celui-ci. Il a donc peu ou pas de fonctionnalités propres quand on le considère comme un système indépendant.

le DSKY (tout comme l'AGC) ont été conçus au laboratoire d’instrumentation du MIT (MIT/IL pour Massachusetts Institute of Technology / Instrumentation Laboratory) sous la direction de Charles Stark Draper.

C'est l'ingénieur Ramon Alonso et son équipe qui en sont les concepteurs. Le matériel de vol a été fabriqué par la société Raytheon. Ramon Alonso, né en Argentine et fils de linguiste, a appris l'anglais comme seconde langue. C'est cette expérience qui l'inspire à utiliser un format de nom et de verbe pour communiquer avec l'ordinateur. Utiliser le DSKY est comme avoir une conversation avec l'AGC en utilisant de minuscules phrases grammaticales, mais le DSKY n'était jamais censé voir le jour. C'était juste un prototype pour essayer de démontrer le type d'interface dont ils auraient besoin pour les missions Apollo. L'ingénieur logiciel Alan Green et son équipe ont développé le programme qui prend en charge les communications des astronautes avec l'ordinateur.

Le DSKY est un terminal petit et simple par rapport aux normes actuelles. Il est intéressant car il n'a que quelques relais de verrouillage pour piloter les affichages de segments et une simple logique de type transistor pour générer des codes-clés à partir du clavier.

Aujourd'hui, cet appareil serait fabriqué à l'aide peut-être d'un seul micro-contrôleur et serait très simple. Je reste persuadé que même de nos jours, de nombreux astronautes souhaiteraient disposer d'un appareil similaire pour communiquer avec l'ordinateur de guidage, au moins comme dispositif de secours, en cas de problème avec les écrans tactiles modernes et les écrans haute résolution. Sa petite taille, sa simplicité et son intégration au logiciel et au matériel Apollo maintiendront également cet appareil populaire à l'avenir.

Il y a 2 DSKY dans le module de commande, le premier sur le tableau de bord principal (Main Display Console) dit "DSKY principal" entre les sièges du pilote CM et du commandant de mission et le second dans la baie d'équipements inférieure (du côté droit du groupement optique, espace "réservé" du navigateur : la station de navigation) dit "DSKY de navigation". Les trois DSKY (en comptant celui du LM) sont électriquement identiques. En tant que tel, les deux dans le CM sont interchangeables.

Prototype d'un DSKY |

Ci-dessus une vidéo (en vol) sur l'utilisation du DSKY. |

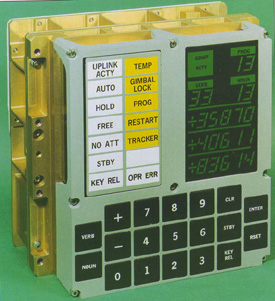

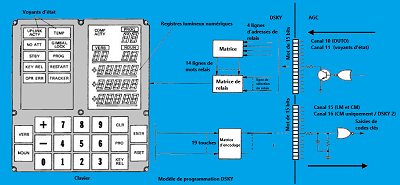

Le DSKY (schéma ci-dessous à gauche) est divisé en trois sections : le tiers inférieur pour le clavier et deux autres pour les affichages. La section clavier contient 19 touches (10 touches et 9 "opération" : VERB, NOUN, CLR, PRO, KEY REL, ENTR, RESET, + et -) le mot, le signe ou le numéro d'une touche est toujours illuminé. Les 19 touches sont codés dans une valeur de frappe de 5 chiffres et contrôlés par l'AGC. La partie supérieure gauche comporte un ensemble de 14 indicateurs d'avertissement et d'alerte, des panneaux rectangulaires avec du texte inscrit dessus qui s'allument en blanc ou en jaune. Le coin supérieur droit a un panneau électroluminescent qui comporte 4 indicateurs d'affichage d'opération (zones d'affichage de 2 digits pour les verbes, les noms courants ainsi que le programme) et 18 indicateurs d'affichage de données (3 zones d'affichage de 5 digits appelés REGISTERS, pour registres) sur la droite. Le DSKY possède également un panneau d'avertissement sur sa gauche. Il mesure 21,6 cm sur 21,6 cm par 18 cm de profondeur, pèse environ 8 kg et est alimentée en 28 V et 14 V CC par l’ordinateur. Un signal d’horloge de 800 Hz est utilisé, qui permet de générer une tension de 250 VAC (Volt Alternatif Courant) avec une fréquence de 400 Hz pour alimenter l’affichage.

Un connecteur à 91 broches (J9), une vanne de remplissage, utilisée pour pressuriser le boîtier avec de l'azote sec (une caractéristique courante dans les systèmes électroniques du Block II) pour éliminer les risques d'étincelles dans l'environnement à oxygène pur de la cabine et une alimentation sont également montés à l'arrière de chaque DSKY. Le connecteur à 91 broches connecte le DSKY à l'AGC, au PGNCS et à d'autres systèmes du vaisseau.

Les connexions se font via le faisceau d'interconnexion "PGNCS A" pour le DSKY du tableau de bord principal et via le faisceau d'interconnexion "PGNCS H" pour le DSKY du poste de navigation. Une valve pneumatique de remplissage est utilisée pour pressuriser le DSKY à une atmosphère. Le module d'alimentation fournit la tension nécessaire pour allumer les indicateurs d'affichage.

L'échange de données entre l'équipage et l'AGC est généralement déclenché par une action de l'équipage, mais il peut également l'être par des programmes informatiques internes. Les informations échangées sont traitées par le programme DSKY.

Ce programme permet les cinq modes de fonctionnement suivants :

• Affichage des données internes. Un affichage ponctuel et un affichage à mise à jour périodique (appelé moniteur) sont tous deux fournis.

• Chargement des données externes. Au fur et à mesure que chaque caractère numérique est saisi, il est affiché à l'endroit approprié du panneau d'affichage.

• Appel et contrôle du programme. Le DSKY est utilisé pour lancer une classe de routines qui ne concernent ni le chargement ni l'affichage. Certaines routines nécessitent des instructions de la part de l'opérateur pour déterminer s'il faut s'arrêter ou continuer à un point donné.

• Changement de mode majeur. Le déclenchement de phases de mission à grande échelle peut être commandé par l'opérateur.

• Affichage de l'avertissement et de l'état du PGNCS. Le DSKY est utilisé pour afficher l'état de l'ISS, de l'OSS et du CMC et pour indiquer les mises en garde relatives au matériel et aux logiciels.

Le DSKY peut également être utilisé par des programmes internes calculés pour des sous-programmes. Cependant, toute action de l'opérateur sur le clavier (à l'exception de RSET) empêche l'utilisation du DSKY par les routines internes. L'opérateur conserve le contrôle du DSKY jusqu'à ce qu'il souhaite le relâcher. Il est ainsi assuré que les données qu'il souhaite observer ne seront pas remplacées par des affichages de données initiés en interne. En général, il est recommandé à l'opérateur de libérer le DSKY pour un usage interne lorsqu'il en a temporairement terminé avec lui : cela se fait en appuyant sur la touche KEY REL.

La section électroluminescente utilise un courant alternatif de 250V 800 Hz pour exciter les segments et les faire briller en vert, à 5300 angströms. La haute tension est commutée par de nombreux petits relais à l'intérieur de l'affichage, permettant à l'AGC d'utiliser une faible tension continue pour commuter la haute tension alternative vers les éléments d'affichage. Il fallait 37 relais pour alimenter un seul des chiffres signés à cinq chiffres.

Les voyants d'avertissement et d'alerte sont des ampoules à incandescence ordinaires de 5V CC, commandées par des relais qui sont à leur tour alimentés par l'AGC. Les voyants d'état ont un fond blanc, tandis que les voyants d'avertissement et d'alerte s'allument en jaune.

Les claviers (2 DSKY) sont rétro-éclairés par des lampes 110V AC 400 Hz, utilisant le bus AC standard du vaisseau spatial.

Voyants indicateurs de mise en garde et d'alarme sur le côté gauche du DSKY

Sur les DSKY équipant le module de commande, seuls dix voyants indicateurs sont utilisés. Sur la photo du DSKY (ci-dessus à droite) vous pouvez voir que l'espace vide où se trouveraient les quatre autres voyants sur un DSKY équipant le LM est simplement recouvert.

- UPLINK ACTY : allumé lorsque l'ordinateur reçoit des données du sol (message numérique complet de 16 bits), ou pendant le programme de navigation de rendez vous.

- TEMP : s'allume lorsque l'AGC reçoit un signal du contrôle de la température de l'IMU: celle ci est supérieure à sa norme de fonctionnement (de 52,38° Celsius à 56,83° C).

- NO ATT : allumé quand le sous-système inertiel ne fournit aucune indication.

- GIMBAL LOCK : s'allume quand l'angle d'un cardan de la plateforme inertielle est supérieur à 70°.

- STBY : allumé lorsque l'ordinateur est en mode "attente" (standby).

- PROG : allumé, il Indique que la vérification du programme a échoué. Cet indicateur est contrôlé par le programme du CMC.

- KEY REL : allumé lorsqu'un un affichage interne désire l'utilisation du DSKY.

- RESTART : s'allume lorsque l'AGC détecte un échec provisoire de matériel ou de logiciel (redémarrage du matériel et réinitialisation).

- OPR ERR : s'allume quand l'opérateur (astronaute) saisit un ordre incorrect sur le clavier du DSKY.

- TRACKER : allumé lorsque l'AGC reçoit un signal de l'OCDU (Optical Coupling Data Units) indiquant un échec.

Indicateurs d'affichage de fonctionnement

- COMP ACTY : s'allume lorsque l'AGC exécute une séquence interne.

- PROG : indique la ou les fonctions du programme en cours d’exécution dans le CMC.

- VERB : affiche le code du verbe saisi au clavier.

- NOUN : affiche le nom du code entré au clavier.

Indicateurs d'affichage de données

- Indications d'affichage des données : Les données affichées sont précédées d’un signe + ou - lorsqu’elles sont en base décimale. En revanche, l’absence de signe indique que les données sont exprimées en base octale.

INTERFACES D'ENTRÉE/SORTIE DU PROGRAMME DU SYSTÈME DE CLAVIER ET D'AFFICHAGE

Les entrées externes du programme du système de clavier et d’affichage sont le clavier à fil direct et la liaison montante. La sortie est assurée par le panneau d’affichage électroluminescent.

Clavier à fil direct

Le clavier du DSKY comprend les touches suivantes :

- KEY REL : libère le contrôle du clavier pour permettre l’affichage des informations générées par une action programmée.

- STBY : déclenche la condition de redémarrage du CMC et place ce dernier en mode basse consommation. Le fonctionnement normal peut être repris en appuyant de nouveau sur STBY.

- RSET : efface les indicateurs de mise en garde et lindicateur OPR ERR.

- CLR : efface les données contenues dans le registre de données actuellement utilisé.

- VERB : conditionne l'AGC pour interpréter les deux prochains caractères numériques comme une demande d'action.

- NOUN : conditionne l'AGC pour interpréter les deux prochains caractères numériques comme un code d'adresse.

- ENTR : informe l'AGC que les données saisies sont complètes et qu'il doit exécuter la fonction demandée.

- + key : saisit le signe positif pour les données décimales.

- - key : saisit le signe négatif pour les données décimales.

- Touches de 0 à 9 : saisissent les données, le code d'adresse et le code de demande d'action dans l'AGC.

À chaque pression d’une touche, une tension continue de +14 V est appliquée à un encodeur à diode qui génère un code unique de cinq bits correspondant à cette touche. Il n’existe toutefois pas de code à cinq bits associé à la touche PRO. Chaque caractère est donc représenté par un code binaire à 5 bits (voir tableau ci-dessous).

TOUCHE |

CODE |

0 |

10000 |

1 |

00001 |

2 |

00010 |

3 |

00011 |

4 |

00100 |

5 |

00101 |

6 |

00110 |

7 |

00111 |

8 |

01000 |

9 |

01001 |

VERB |

10001 |

RESET |

10010 |

KEY REL |

11001 |

+ |

11010 |

- |

11011 |

ENTER |

11100 |

CLEAR |

11110 |

NOUN |

11111 |

Les touches contiennent des contacts de commutation, activés de manière à empêcher la génération de deux codes en même temps. Le code du clavier est transmis à l'ordinateur par une liaison à 5 fils et est placé dans les bits 1 à 5 du canal d'entrée approprié.

CSM : chaque pression sur une touche du DSKY du tableau de bord principal (MDC) place le code associé à cette touche dans les positions de bits 1 à 5 du canal d'entrée 15 et active une demande d'interruption du programme KEYRUPT1 (INTERRUPT KEYRUPT1).

Chaque pression sur les touches du DSKY de la station de navigation place le code associé dans le canal 16 et active une demande d'interruption du programme KEYRUPT2 (INTERRUPT KEYRUPT2).

LM : chaque pression sur une touche du clavier du DSKY active une demande d'interruption du programme KEYRUPT1 (INTERRUPT KEYRUPT1) et place le code clé dans le canal 15.

Le programme KEYRUPT approprié récupère le code clé et introduit une demande auprès de la routine exécutive qui décode et assimile le code clé (CHARIN). Un "RESUME" est ensuite exécuté, mettant fin au KEYRUPT

Le saviez-vous ?? Les canaux sont donnés ici sous forme de nombres octaux.. comme la plupart des nombres dans la programmation de l'Apollo AGC. Ainsi, le canal 016 est en fait 8+6 = 14 en décimal et 0x0E en hexadécimal. L'octal est une bizarrerie pour de nombreux programmeurs actuels qui sont plus habitués au codage hexadécimal depuis les microprocesseurs des années 1970. |

"CHARIN" qu'est ce que c'est ? "Charin" ou "Pinball CHARIN" est une routine informatique qui traite les données. Elle catégorise la frappe comme un "Verb" (verbe) ou un "Noum" (nom), un chiffre ou l'une des autres touches d'opération, et détermine le traitement à effectuer. L'appui sur la touche "Verb", par exemple, active des drapeaux indiquant que les caractères suivants doivent être interprétés comme un code "Verb", et active des bits dans le tampon de sortie de l'affichage, DSPTAB (mémoire effaçable), pour faire clignoter les champs "Verb" et "Noum". La vérification de l'intégrité de la saisie est effectuée en premier. Les frappes non valides, telles que l'appui sur une touche non numérique alors que des données numériques sont attendues, mettent fin à CHARIN et allument le voyant "OPR ERR".

Lorsque des données numériques sont saisies dans le DSKY, elles s'affichent d'abord dans le chiffre le plus à gauche du "VERB", du "Noum" ou du registre, et chaque nouveau chiffre apparaît successivement vers la droite. Cela diffère du cas habituel où chaque frappe déplace l'affichage existant vers la gauche, le nouveau chiffre étant inséré dans la position la plus à droite. Ce n'est qu'après avoir appuyé sur la touche Entrée que l'interprétation des données commence.

Uplink inputs, les entrées de la liaison montante

La liaison montante est le système de télémétrie numérique qui envoie des informations du sol à l'ordinateur embarqué. C'est simplement un moyen d'avoir un clavier à distance au sol, qui peut transmettre par radio des frappes à l'AGC à bord du vaisseau spatial comme s'il s'agissait d'un DSKY. En d'autres termes, les seules données que la liaison montante peut transmettre correspondent aux codes du clavier DSKY. Ces codes sont identiques aux codes DSKY de 5 bits, mais si (par exemple) un code clé de 5 bits de bits B5 B4 B3 B2 B1 doit être transmis, il est censé être présenté dans le format de 16 bits suivant pour la liaison montante : 1 B5 B4 B3 B2 B1 B5 B4 B3 B2 B1 B5 B4 B3 B2 B1.

Après la détection de la liaison montante, le témoin d'activité UPLINK ACTY du DSKY s'allume (allumé par tous les programmes UPRUPTs) pour informer les astronautes qu'une liaison montante est en cours, et il est reste allumé dans la plupart des cas jusqu'à ce que la liaison montante envoie un code clé KEY REL pour "libérer" le clavier relié à la liaison montante.

Un UPRUPT est exécuté à chaque fois qu'un message de liaison montante de 15 bits est assemblé dans le registre UPLINK. Le programme UPRUPT lit ce message et teste le format WWW. (Il s'agit d'un message à code clé de 5 bits, son complément se trouvant dans les 5 bits du milieu et l'original dans les 5 bits de poids fort). Si le test WWW est réussi, une demande exécutive est placée pour que CHARIN assimile le code clé de 5 bits. Ensuite, un RESUME est exécuté, mettant fin à l'UPRUPT.

Par contre, si le test WWW échoue, un verrouillage de programme est activé pour bloquer toute nouvelle acceptation de messages de la liaison montante. Ce blocage est levé par l'envoi du code de réinitialisation par l'intermédiaire de la liaison montante. Il est important d'envoyer une chaîne d'au moins 15 zéros avant la réinitialisation pour éliminer tous les "uns" qui pourraient être laissés dans la liaison montante en raison d'une désynchronisation.

Notez que "CHARIN" ne fait aucune distinction entre les entrées provenant du clavier et celles provenant de la liaison montante.

Il y a un interrupteur à bascule qui est utilisé soit pour accepter les entrées de la liaison montante, soit pour bloquer la liaison montante. En position bloquée, l'opérateur a choisi de n'accepter aucune entrée de type clavier depuis le sol.

Ces codes entrent dans l'ordinateur par les bits 1-5 du canal 15 ou 16 (CSM ou LM). Le MSB (Most Significant Bit pour bit de poids fort) est placé dans le bit 5 ; le LSB (Least Significant Bit pour bit de poids faible) dans le bit 1.

LE DIALOGUE AVEC L'AGC VIA LE DSKY

Une interface bien conçue doit établir un "langage" entre l'utilisateur et la machine : un langage qui convertit les besoins et les souhaits de l'utilisateur en demandes facilement compréhensibles par le logiciel. Avec brio, le "langage" de l'AGC a été basé sur la façon dont les humains communiquent. |

Le dialogue est assez simple, il prend généralement la forme d'une combinaison d'un verbe (VERB), suivi d'un nom (NOUN). Les verbes, les noms ainsi que les programmes sont identifiés par des codes uniques à deux chiffres. Il y en a beaucoup à retenir, environ 45 programmes, 80 verbes, 90 noms. Une fois le verbe et le nom chargés dans les registres, une pression sur la touche Entrée indique que la saisie est acceptable et prête à être traitée. Voici un exemple de ce que pourrait être une demande DSKY (exemple : heure d'affichage de la prochaine combustion du moteur) :

• Verbe 06, Nom 33, Entrée ou, en abrégé, V06N33E.

• Taper le verbe 06 (Affiche les données décimales), le nom 33 (Temps d'allumage), terminer en appuyant sur la touche Entrée.

La définition "VERB" fait appel à un type d'action (ensembles de commandes), et la définition "Noun" précise sur quel type de donnée (ordre spécifique), ou sur quel composant ou système cette action doit être effectuée.

Dans le cas d'ordres plus complexes, le système attend que chaque donnée soit saisie et peut exécuter des routines préenregistrées (modes majeurs) permettant ainsi de gagner du temps.

Malgré les obstacles, le DSKY s'est révélé être un outil fiable et a contribué à toutes les missions habitées sur la Lune. De ses origines linguistiques modestes à un mémorial dans les étoiles, le DSKY est responsable du succès des missions Apollo

Le saviez vous ? Aujourd'hui, beaucoup de gens confondent le DSKY avec l'AGC, bien qu'il ne s'agisse que de l'interface (d'ailleurs, je ne peux m'empêcher de mentionner que le programme chargé de gérer l'écran du DSKY s'appelait "Pinball Game Buttons and Lights").

Le saviez vous (2) ? Malgré ses avantages, lAGC nest pas une bête facile à dominer. Pour aligner la centrale inertielle, il faut entre 30 et 130 pressions sur les touches du DSKY et plus de dix mille frappes peuvent être atteintes lors dun voyage vers la Lune. La conséquence est que léquipage a passé un pourcentage significatif de son temps dans lespace à taper des instructions sur le panneau DSKY.

L'ALIMENTATION ÉLECTRIQUE DU DSKY

L’alimentation du DSKY reçoit en entrée du +28 VDC et du +14 VDC en provenance de l’alimentation du CMC (AGC), ainsi qu’un signal de 800 Hz issu du minuteur du CMC. Elle délivre en sortie une tension de 250 volts à 800 Hz utilisée pour l’éclairage des registres d’affichage du DSKY.

Ce circuit d’alimentation comporte trois amplificateurs push-pull à couplage par transformateur, un réacteur saturable, et un pont redresseur en onde complète. L’entrée du premier étage est une onde carrée à 800 Hz superposée à un niveau de +14 VDC. Ce niveau continu est commandé par le réglage de la luminosité sur le panneau de commande des astronautes. Les deux transformateurs élèvent la tension appliquée à leurs enroulements primaires. Les trois amplificateurs accroissent également l’amplitude de la tension d’entrée. La sortie du troisième amplificateur push-pull est appliquée au réacteur saturable.

Le réacteur saturable et le circuit qui lui est associé régulent la tension appliquée aux registres d’affichage. Ces derniers constituent une charge capacitive variable, fonction du nombre d’indicateurs activés. Les variations de cette charge capacitive sont répercutées sur l’enroulement de commande du réacteur par l’intermédiaire du pont redresseur. Lorsque le nombre d’indicateurs allumés augmente, la tension appliquée à l’enroulement de commande augmente elle aussi. Cette hausse fait entrer le réacteur plus profondément en saturation, ce qui permet de maintenir la tension de sortie relativement constante. Si la charge diminue, la tension de l’enroulement de commande baisse, et le réacteur devient moins saturé.

Enfin, le +28 VDC du CMC est filtré pour alimenter les relais du DSKY.

L'Apollo Guidance Computer (AGC) est un ordinateur numérique embarqué conçu pratiquement à partir de zéro spécifiquement pour être utiliser à bord du vaisseau spatial Apollo afin de soutenir les atterrissages lunaires. Ce n'est pas du tout un ordinateur à usage général (bien que doté de nombreuses caractéristiques de celui-ci). Il n'a pas besoin de s'adresser à un ensemble complexe de périphériques par le biais d'une couche d'abstraction matérielle (2), ni d'analyser des "commandes de style anglais" (English-style commands) ; il n'a pas de langage de programmation de haut niveau à interpréter. Il peut être classé comme ordinateur parallèle, polyvalent ou binaire à nombre entier.Un vaisseau spatial Apollo opérationnel contient deux AGC et trois DSKY : un AGC et deux DSKY dans le CM, un AGC et un DSKY dans le LM. Les deux appareils sont identiques en termes de matériel mais sont reliés à des périphériques partiellement différents et exécutent des logiciels distincts, adaptés à chacun des vaisseaux.

En tant qu'ordinateur de contrôle, son rôle principal est de surveiller le vaisseau lors de son trajet vers la Lune, en gardant la trace de l'endroit où il se trouve et de celui où il va (sous la forme de son vecteur d'état par rapport à l'un des plusieurs points de référence différents, qui changent au fur et à mesure de la mission). L'AGC traite donc non seulement les informations en provenance des deux autres sous-systèmes du GNCS (IMU et optique), mais également d'autres composants du vaisseau, comme par exemple ceux du système de communication (au total 20). Il a la possibilité d'envoyer des signaux au RCS, pour corriger une trajectoire. De même, il gère aussi le temps de poussée du SPS, pour ralentir la vitesse du vaisseau (lors de l'insertion orbitale lunaire par exemple). En tant qu'ordinateur à usage général, il résout les équations de guidage et de navigation requises pour la mission lunaire. L'AGC n'a pas une aussi longue liste de responsabilités que les ordinateurs d'un vaisseau spatial actuel, mais il traite toujours un grand nombre de tâches et est l'objet d'attention constante de l'équipage. Même avec son rôle autonome réduit, le système informatique embarqué d'Apollo peut être considéré comme un contrôleur sophistiqué construit et intégré à part entière au matériel de son véhicule hôte si bien que les concepteurs l'appelle "le quatrième membre d'équipage".

Aperçu des données techniques de l'AGC Block II

Fréquence d'horloge |

1024 MHz |

Longueur du mot |

16 bits |

Temps du cycle mémoire |

11,72 µs (microsecondes) |

RAM |

2048 mots |

ROM |

36864 mots |

Instruction machine |

34 régulier |

Interuptions prioritaires |

11 |

Temps supplémentaire |

23,4 µs (microsecondes) |

Temps de multiplication |

46,8 µs (microsecondes) |

Entrées/sorties |

227 circuits |

Circuits intégrés |

5600 portes |

Consomation électrique |

28 Volts, 70 Watts |

Masse |

31,79 kg |

Volume |

27,5 l |

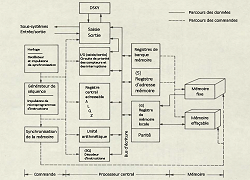

L'AGC comporte trois sections principales (voir schéma ci-dessous), une mémoire, un processeur central et une section de commande. La section mémoire est divisée en deux parties, fixe et effaçable. La section du processeur central comprend un additionneur, un décodeur d'instructions, une commande d'interruption, un décodeur d'adresses de mémoire, un registre tampon local de mémoire et un certain nombre de registres adressables avec des fonctionnalités spéciales ou une utilisation spéciale. L'épine dorsale de l'AGC est l'ensemble de 16 bus d'écriture qui sont les moyens de transférer des informations entre les différents registres de la section centrale.

Noter qu'environ la moitié du schéma d'architecture ci-dessus est occupée par la mémoire, ce qui montre qu'à bien des égards, l'architecture de l'AGC a été conçue autour de sa mémoire.

Outre ses performances techniques et sa compacité, l'AGC doit bien entendu résister sans problème aux énormes contraintes physiques du lancement de Saturn V. Cela est réalisé d'une part par des boitiers stables de l'AGC, d'autre part par des composants extrêmement robustes. Par exemple, la mémoire fixe qui contient tous les programmes de navigation, est basée sur une technologie innovante (pour l'époque) qui permet de construire une mémoire très stable avec un volume pourtant réduit et une densité de stockage élevée.

Le saviez vous ? Si le LVDC (l'ordinateur de Saturn V) échoue en vol, l’AGC peut prendre la relève (voir encadré ci-dessous). Mais si celui-ci échoue également, en dernier recours, le commandant peut théoriquement mettre Saturn V en orbite (contrôler un lanceur de 3 000 tonnes à la main : cela aurait valu la peine d'être vécu.. Ou pas..).

Alors soyons clairs : On pense souvent que les astronautes pouvaient piloter la fusée Saturn V à l’aide de l’AGC. Mais aucun humain ne le pouvait. Une fois le lancement effectué, la Saturn V était entièrement pilotée automatiquement par l’ordinateur du lanceur, appelé LVDC (Launch Vehicle Digital Computer), situé dans l’Instrument Unit (IU). Pendant l’ascension, les astronautes comme le sol recevaient des données de télémétrie provenant de l’ordinateur du lanceur. Au moment du lancement, l’ordinateur du module de commande (CMC, aussi appelé AGC) lançait un programme appelé Earth Orbit Insertion Monitor (P11), qui surveillait le déroulement du vol et détectait les écarts éventuels, mais ne pouvait en aucun cas corriger un problème de guidage. Ni l’ordinateur ni les astronautes ne pouvaient diriger Saturn V pendant l’ascension. Les seuls moyens d’action de l’équipage et du sol pendant cette phase étaient les suivants : • L’équipage pouvait déclencher manuellement la séparation entre le deuxième et le troisième étage. Ce n’est qu’une fois le troisième étage en orbite avec le vaisseau que certaines commandes devenaient accessibles : le sol pouvait alors envoyer des commandes, et les astronautes pouvaient envoyer des commandes via l’ordinateur du module de commande et influencer le guidage, sans pour autant piloter directement la fusée. La réponse est donc NON : pendant le lancement et l’ascension, les astronautes n’avaient pratiquement aucun contrôle sur le lanceur. Une source de confusion vient d’un interrupteur du module de commande appelé « Launch Vehicle Guidance », qui permet de sélectionner si le guidage est assuré par le LVDC ou par le CMC. Cependant, cet interrupteur reste verrouillé jusqu’à l’événement T5. En effet, dans le LVDC, les événements sont organisés autour de sept jalons : • T1 : décollage Par exemple, dans la chronologie d’Apollo 8, l’allumage du troisième étage s’est produit 8 minutes et 44 secondes après le lancement, mais dans le calcul interne de l’ordinateur, il est considéré comme se produisant 4 secondes après T4. Tout dans l’ordinateur est référencé par rapport à ces sept événements critiques. Le point essentiel est que les astronautes ne peuvent intervenir qu’à partir de T5, c’est-à-dire lorsque le lanceur a atteint l’orbite et que le troisième étage est arrêté. Le lancement est alors terminé, même si le troisième étage doit encore fonctionner par la suite. |

CONFIGURATION ET ARCHITECTURE GÉNÉRALE

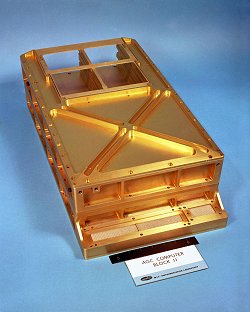

La version Block II est la seule ayant volée vers la Lune. Conçue en 1966, elle conserve l'architecture de base du Block I. L'unité mesure 61 par 32 par 15 cm, pèse ~32 kg et requière 28V et 70W.

L'ordinateur de vol d'Apollo est le premier à utiliser des circuits intégrés (ICs pour Integrated Circuits) dans le spatial. Il est fonctionnellement divisé en sept domaines :

- minuterie (timer) : pour les impulsions de synchronisation.

- générateur de séquences (sequence generator) : régule l'exécution des instructions de la machine par des impulsions de commande.

- unité centrale de traitement (central processor) : calculs.

- mémoire : divisée en mémoire morte (ROM) et mémoire inscriptible (RAM).

- contrôle des priorités (priority control) : contrôle des priorités des différentes opérations.

- entrée-sortie.

- alimentation en énergie (power) : alimentation en 4 volts et 14 volts à partir des piles à combustible.

L'architecture de l'AGC est une architecture Von Neumann (3). Bien que l'AGC soit spécialement conçu pour la navigation spatiale, il s'agit d'un ordinateur polyvalent capable d'assumer les fonctions les plus diverses, comme par exemple la prise en charge du pilotage du lanceur Saturn V ou l'exécution d'interruptions de mission, qui posent au système des exigences différentes selon la phase de vol en cours. En outre, la gestion des priorités constitue une procédure d'ordonnancement encore actuelle aujourd'hui, qui est non seulement très moderne dans les années 1960, mais qui n'a jamais été utilisée auparavant pour un ordinateur de navigation dans un avion ou un vaisseau spatial. Il n'existe tout simplement pas d'ordinateurs suffisamment puissants pour la navigation spatiale et aussi compacts que l'AGC.

Le corps de l'AGC se compose de deux moitiés, appelées plateau A et plateau B. Ce châssis réalisé en magnésium est usiné par fraisage. En effet, des études de conception visant à réduire la masse, dans la mesure du possible, permettent de remplacer les alliages d'aluminium originaux par des alliages de magnésium, ce qui a pour effet d'économiser 5,44 kg (12 lb). Toutefois, le magnésium nécessite une finition qui doit répondre aux exigences de l'engin spatial en matière de contamination et de résistance à la corrosion. Pour cela, les modules ou les surfaces à l'intérieur de l'AGC sont anodisés. Toutes les surfaces exposées à l'environnement du vaisseau spatial sont peintes en plus de l'anodisation. Les peintures doivent être exemptes d'odeurs et offrir une surface à faible émissivité pour le contrôle thermique du vaisseau spatial. Les surfaces visibles une fois installées dans le CM doivent être assorties au gris foncé de l'intérieur de l'habitacle. Les trous de vis et les surfaces autour des trous ne sont pas peints mais traités avec une anodisation conductrice pour assurer la liaison électrique des interfaces entre les plateaux, les entretoises, les couvercles et l'AGC à la plaque froide du vaisseau spatial. Dans le cas de l'AGC et du matériel de montage du vaisseau spatial, des boulons en acier avec des tiges recouvertes de Téflon et des rondelles en aluminium sous leurs têtes sont nécessaires pour éviter la corrosion, car le matériel de montage est composé de métaux dissemblables (magnésium et acier). La conception du Block II répond également aux nouvelles exigences en matière de résistance aux interférences électromagnétiques et d'ignifugation.

Le plateau A contient trente et un modules : vingt quatre modules logiques, cinq d'interface et deux d'alimentation à découpage qui convertissent les 28 volts du vaisseau spatial en 4 et 14 volts pour le fonctionnement de l'AGC. Tous les modules sont montés sur le plateau, puis enrobés d'un composé silastique. Le plateau A comporte trois connecteurs inter-plateaux : A61, A62, A63 et deux connecteurs à l'arrière. Un connecteur arrière à 360 broches (A51) relie le CMC, par l'intermédiaire du harnais d'interconnexion A du PGNCS, à la source d'alimentation principale de 28 Vdc, aux DSKY (les 2), aux autres parties du PGNCS et aux autres systèmes de l'engin spatial. Un connecteur arrière à 144 broches (A52) assure l'interface avec l'équipement de soutien au sol utilisé pour tester le CMC.

Le plateau B contient dix-sept modules (oscillateur, dispositifs d'alarme analogiques, mémoire effaçable, l'électronique de mémoire...), dont six modules de mémoire à cordes. Tous les modules (plateau A et B) sont hermétiquement scellés et encastrés dans les plateaux, à l'exception des modules de mémoire corde qui sont branchés à l'avant de l'AGC et fixés par des vis de calage. Ce montage offre un bon chemin thermique entre les modules et leurs supports. Le plateau est à son tour vissé sur une plaque de refroidissement, d'où s'opère un échange thermique (suppression de la chaleur émise par les composants). Le cadre fournit également des joints d'étanchéité à l'humidité pour tout le câblage interne et les connecteurs. Le plateau B possède trois connecteurs inter-plateaux : B61, B62, et B63.

L’AGC est complètement hermétique pour se prémunir des conditions environmentales de la cabine (oxygène pur, forte humidité) et ne contient aucune pièce à entretenir. Malgré cela, les ingénieurs craignent que les nouveaux microcircuits numériques ne tombent en panne dans l’espace. Les premières versions permettent donc de remplacer les modules. Dans les versions ultérieures de l'AGC, une fois tout le monde convaincu de sa fiabilité, l'exigence de maintenabilité a été exclue de l'énoncé des travaux ou EdT (4).

Au total, l'appareil contient environ 30 000 pièces. Chaque composant est soumis à un test électrique et à un test d'effort. Tout échec appelle le rejet du composant et de son lot.

Le saviez vous ?? L'AGC n'est peut-être pas doté de grandes capacités (vitesse de calcul et mémoire), mais en revanche, il est d'une fiabilité extrême. Sur les 42 systèmes Block II livrés et sur un total de 11 000 heures d'exposition aux vibrations et aux cycles thermiques, plus 32 500 heures de fonctionnement normal, seules 4 défaillances matérielles ont été observées, dont aucune ne s'est produite au cours de missions lunaires réelles. Une estimation prudente du temps moyen entre les défaillances (MTBF pour Mean Time Between Failures) de l'AGC a été calculée par la suite comme étant supérieure à 40 000 heures, soit plus d'un ordre de grandeur de mieux que les machines typiques de l'époque.

LA MÉMOIRE

Un peu d'histoire : l'évolution de la mémoire dans l'AGC reflète une augmentation constante de sa taille en réponse aux exigences croissantes de la mission. Lorsqu’on conçoit ou acquiert un système informatique pour une application spécifique, il est particulièrement difficile d’estimer précisément les besoins en mémoire. La NASA et ses sous-traitants informatiques ont d’ailleurs toujours eu du mal à évaluer ces besoins de façon adéquate. L’AGC disposait d’une mémoire permanente (fixe) et d’une mémoire effaçable, cette dernière étant rapidement augmentée par rapport aux prévisions initiales. L’ordinateur d’Apollo utilisait la mémoire effaçable pour stocker les résultats intermédiaires des calculs, des données telles que la position du vaisseau spatial, ou encore comme registres pour les opérations logiques. Ces mémoires contenaient également les données et routines nécessaires à la préparation de l’ordinateur lors de sa première mise sous tension. La mémoire fixe, quant à elle, contenait les programmes qui ne nécessitaient aucune modification durant la mission. Les temps de cycle de ces mémoires étaient égaux afin de simplifier leur utilisation.

Initialement, la conception originale du MIT prévoyait seulement 4K mots de mémoire fixe et 256 mots de mémoire effaçable, avec l’idée d’utiliser deux ordinateurs pour assurer la redondance. En juin 1963, ces chiffres avaient évolué à 10K mots de mémoire fixe et 1K mots de mémoire effaçable. La prochaine étape fut d’atteindre 12K mots de mémoire fixe, le MIT restant convaincu que les besoins pour une mission lunaire autonome pouvaient être maintenus sous la barre des 16K mots. Finalement, la mémoire fixe passa à 24K puis à 36K mots, tandis que la mémoire effaçable fut configurée pour contenir 2K mots.

Le manque de mémoire engendra cependant des difficultés constantes et importantes dans le développement des logiciels, malgré une augmentation de la mémoire fixe d’un facteur 18 et de la mémoire effaçable d’un facteur 16 par rapport aux prévisions initiales. Une partie des problèmes logiciels était liée à des fonctions et caractéristiques qui durent être abandonnées à cause de la taille limitée des programmes, tandis qu’une autre venait des contraintes d’adressage déjà évoquées. Si les concepteurs avaient su dès le départ qu’une telle capacité mémoire serait nécessaire, ils n’auraient peut-être pas opté pour une taille de mot aussi courte, car un mot de 24 bits aurait permis d’adresser directement une banque de 36K mots, avec une marge suffisante pour une liste complète de codes d’instruction.

L’une des raisons majeures de la sous-estimation des besoins en mémoire vient du fait que la NASA n’avait pas fourni de spécifications détaillées sur les fonctions précises que l’ordinateur devait assurer. Elle avait seulement défini le besoin général et les grandes lignes des tâches, et le MIT avait reçu un contrat basé sur un énoncé très sommaire des exigences dans l’appel d’offre.

L'AGC est un ordinateur numérique doté de deux types de mémoire distincts : une mémoire de travail à noyau de ferrite à courant coïncident ( RAM ou Random Access Memory pour mémoire à accès aléatoire [lecture/écriture], également appelée mémoire vive, mémoire effaçable ou mémoire à noyaux magnétique) et une mémoire à lecture non destructive destiné au stockage des programmes ( ROM ou Read Only Memory pour mémoire à lecture seule aussi appelée Core Rope Memory pour mémoire à corde ou encore mémoire morte). Cette dernière est de type transformateur (terme générique que nous détaillerons plus loin) et contient les informations câblées directement. La différence logique entre ces deux mémoires réside dans le fait que le contenu de la ROM ne peut être modifié par les programmes en cours d’exécution. La mémoire à cordes est fabriquée (information câblée) sous forme modulaire, chaque module contenant environ 6K mots (kilomots), et peut être connecté sur l'ordinateur. L’AGC peut accueillir jusqu’à six de ces modules, ce qui porte sa capacité maximale de mémoire fixe à environ 36K mots. Cette architecture présente deux caractéristiques remarquables. D’une part, la mémoire vive est conçue pour résister à des températures comprises entre 0 et 70°C. D’autre part, la mémoire à cordes offre une très haute densité de stockage. Grâce à cela, l’ordinateur dispose d’une grande capacité mémoire tout en restant compact. Par ailleurs, cette insensibilité à la température permet à l’AGC de fonctionner efficacement avec une température de plaque froide comprise entre 0 et 35 °C.

Le saviez vous ?? Les instructions de l'ordinateur peuvent adresser des registres situés dans l’un ou l’autre type de mémoire, et les programmes peuvent être stockés dans l’une comme dans l’autre.

Anecdote : Les premiers prototypes de ROM avaient un seul faisceau de fils, rappelant une corde, d’où le nom « mémoire à corde ». La version finale n’a plus cette apparence, mais le nom est resté.

LA MÉMOIRE EFFAÇABLE OU RAM (Random Access Memory)

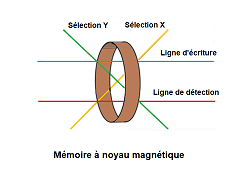

La mémoire effaçable est héritée de son ancêtre, le transistor logique à noyau. Il s'agit d'un réseau conventionnel bidimensionnel de noyaux de ferrite à courant coïncident dont le composé de ferrite permet de combiner une grande rectangularité et une sensibilité relativement faible à la température. De plus, les circuits de transistors en silicium, qui pilotent la mémoire, varient normalement avec la température de manière à répondre aux exigences des cœurs sur une large plage, de 0° à 70°C, ne nécessitant ainsi aucun circuit spécial pour la compensation de température. La sélection par courant coïncident permet de réduire le nombre de circuits de sélection, au prix d'une vitesse moindre par rapport à la sélection linéaire (mot). Ceci est avantageux pour l'ordinateur, où le temps de cycle mémoire est déjà long, en grande partie à cause de la mémoire fixe. La matrice de 2048 mots est câblée en plans de 32 x 64, sans épissures dans les fils, pour une fiabilité maximale. Les plans sont pliés pour tenir dans un module de 147 cm3 (9 in3) avec deux diodes pour chaque ligne de sélection. Des courants bidirectionnels sont générés dans chaque fil de sélection par un réseau de commutation à transistors à double extrémité.

La sélection d'un fil sur 32 est effectuée par 12 circuits de commutation dans un réseau 8 x 4 ; la sélection d'un fil sur 64 est effectuée dans un réseau 8 x 8. Le fonctionnement du réseau de commutation est illustré ci-dessous (à gauche). Les transistors de commande des noyaux sont commandés par des noyaux magnétiques, qui offrent deux avantages : leur petite taille et le stockage de l'adresse pour la régénération des données. Là encore, cette économie de circuit se fait au détriment de la vitesse. La synchronisation des courants, qui actionnent les noyaux de commutation, est basée sur la durée du courant d'écriture dans la matrice de mémoire, et est de 2 µs. Deux pilotes de courant avec des temps de montée contrôlés, un pour la lecture et un pour l'écriture, sont utilisés sur chacun des deux réseaux de sélection des pilotes. Seize autres pilotes de ce type sont utilisés pour piloter les lignes de chiffres qui contrôlent la phase d'écriture du cycle de la mémoire. L'amplitude du courant est régie par la chute de tension directe e2 de la figure ci-dessous (à droite) aux bornes d'une jonction en silicium et de la résistance d'émetteur Rg, de sorte que la compensation de la force coercitive du noyau de ferrite en fonction de la température est assurée sans complexité supplémentaire dans le circuit.

Le signal de sortie des noyaux de mémoire a une amplitude d'environ 50 millivolts. Le couplage par transformateur aux amplificateurs de détection assure une réjection du bruit en mode commun et un gain de tension de 2. Les amplificateurs de détection (voir figure ci-dessous) comportent un premier étage différentiel fonctionnant en mode linéaire (classe A). Un deuxième étage assure la discrimination de seuil, le redressement et le déclenchement ou le stroboscope. Trois tensions de référence sont générées pour les amplificateurs de détection par un circuit dont les caractéristiques de température compensent les changements d'amplitude et de bruit dans la mémoire.

Les amplificateurs de détection à circuit intégré ont certains avantages inhérents aux circuits semi-conducteurs à puce unique. Les amplificateurs différentiels posent un problème particulier d'adaptation des composants, à la fois en interne pour obtenir un équilibre dans un seul amplificateur et parmi un groupe d'amplificateurs pour obtenir un comportement uniforme pour des tensions de référence communes. Dans les amplificateurs à composants discrets, beaucoup de temps et d'efforts sont nécessaires pour spécifier et sélectionner des ensembles de composants de circuit adaptés. Dans un circuit intégré, cependant, l'équilibre est facilement atteint en raison de la correspondance extrêmement étroite entre les transistors sur la même puce de silicium. Il en va de même pour l'uniformité d'un amplificateur à l'autre, la différence étant facilement compensée par des résistances d'ajustage et des tensions de référence externes. La petite taille de l'amplificateur de circuit intégré est avantageuse pour obtenir un suivi de température entre les amplificateurs de détection et la mémoire, car il n'est pas difficile de les maintenir à une température proche de celle des noyaux de mémoire. Alors que les amplificateurs de détection ont toujours été le "maillon faible" des systèmes de mémoire des ordinateurs, l'amplificateur de détection intégré a déjà prouvé qu'il était au moins aussi performant que le reste de l'électronique de la mémoire.

Cette mémoire stocke l'information intermédiaire, contient également les données et les routines nécessaires pour préparer l'AGC à être utilisé lors de sa première mise sous tension et a le même temps de cycle que la mémoire fixe. Elle est construite à partir de minuscules anneaux de ferrite appelés noyaux (ou cœurs).

Les noyaux sont disposés dans une grille ou un plan (appelé natte). Chaque plan stocke un bit d'un mot, de sorte qu'un ordinateur de 16 bits utilise une pile de 16 plans de noyaux. Chaque noyau est généralement traversé par 4 fils : des fils X et Y dans une grille pour sélectionner le noyau, une ligne de détection diagonale à travers tous les noyaux pour la lecture, et une ligne d'inhibition horizontale pour l'écriture. Chaque noyau stocke un bit en étant magnétisé dans le sens des aiguilles d'une montre ou dans le sens inverse. Un courant dans un fil passant par le noyau peut magnétiser le noyau, le sens de magnétisation correspondant au sens du courant. Pour lire la valeur d'un noyau, celui-ci est retourné à l'état 0. Si le noyau était à l'état 1 auparavant, le champ magnétique changeant produisait une tension dans le fil de détection enfilé dans les noyaux. Mais si le noyau était à l'état 0 au départ, le fil de détection ne percevait pas de tension. Ainsi, forcer un noyau à 0 a révélé l'état précédent du noyau (mais l'a effacé dans le processus).

Le saviez vous?? Les noyaux utilisés pour la mémoire effaçable sont des mini-aimants bistables. L'une de leur principale propriété est l'hystérésis. Un courant faible n'a aucun effet sur un noyau ; le courant doit être supérieur à un seuil pour faire basculer le noyau. Cette propriété est très importante car elle permet à une grille de lignes X et Y de sélectionner un noyau dans la grille. En alimentant une ligne X et une ligne Y, chacune avec la moitié du courant nécessaire, seul le noyau où les deux lignes se croisent reçoit suffisamment de courant pour basculer et les autres noyaux ne sont pas affectés. Cette technique de "courant coïncident" a rendu la mémoire centrale pratique, car quelques conducteurs X et Y peuvent contrôler un grand plan de noyau. |

Cette mémoire utilise des plans de cœurs, un plan pour chaque bit du mot. L'AGC a 16 plans, chacune contenant 2048 bits dans une grille de 64×32 plans. Notez que chaque natte est constituée de huit carrés de 16×16 (ci-dessous). Il s'agit typiquement de la mémoire électronique qui contient les données en cours de traitement dans un ordinateur, elle est nécessaire au système d'exploitation, à la gestion des processus, à la récupération et aux variables globales pour toutes les phases de la mission. La saisie est "nettoyable" ; ainsi, si les données doivent être conservées, elles sont ré-inscrites à nouveau. Autrement, l'emplacement est "épuré" (en réalité, pour libérer de l'espace mémoire on n'efface pas les données qui s'y trouve, mais on les écrase par de nouvelles données) pour une nouvelle utilisation.

Au milieu de cette maigre quantité de RAM se trouvent, logé au chausse-pied, des zones de mémoire dédiées utilisées par les programmes d'application : le logiciel qui effectue les tâches de guidage et de navigation, l'atterrissage sur la Lune ou le rendez-vous. Les programmes de base disposent chacun d'un nombre "impressionnant" de 7 mots pour les variables temporaires. L'AGC Block II possède 4 kB (en unité moderne) de RAM. Comme pour la ROM, la mémoire centrale est assez insensible aux pertubations extérieures.

C'est une mémoire non volatile, c'est-à-dire une mémoire qui maintient son contenu en l'absence d'alimentation électrique (contrairement à nos RAM d'aujourd'hui).

Anecdote : À l'époque, la plupart des ordinateurs empilent physiquement les nattes les unes sur les autres, mais l'AGC utilise une structure mécanique différente, pliant les nattes pour qu'elles tiennent de manière compacte dans le module. Elles sont pliés en accordéon pour s'adapter parfaitement au module. Une fois pliées, les nattes forment un bloc qui est monté horizontalement dans le module central.

MÉMOIRE À CORDE OU ROM (Read Only Memory)

QU'EST CE QUE C'EST??

Petit rappel et descriptif rapide : avant le développement de la mémoire à semi-conducteurs LSI (Large-Scale Integration ou intégration à grande échelle, suivie ensuite par l'intégration à très grande échelle, ou VLSI pour Very-Large-Scale Integration), le noyau magnétique était la forme prédominante de mémoire vive dans les systèmes informatiques. Des technologies de mémoire morte ont également été développées pour répondre au besoin moindre de mémoires fixes. L'une de ces technologies était la ROM à transformateur en fil tissé. Cette technologie se caractérise par le tissage sélectif de fils à travers des noyaux de transformateur, mais on peut la distinguer en deux techniques : celle du transformateur à impulsions et la technique du noyau de commutation.

COMMENT EST-ELLE FABRIQUÉE ??

Une fois le programme informatique finalisé, il est envoyé à l’usine Raytheon située à Waltham, où des techniciennes recrutées dans l’industrie textile locale pour leurs compétences en couture tissent littéralement le logiciel dans la mémoire en suivant des instructions détaillées. D'autres femmes qualifiées viennent de la Waltham Watch Company, une entreprise qui participe également à la fabrication des gyroscopes de haute précision utilisés dans les missions Apollo. Le processus exige beaucoup de travail et d'attention, il prend environ 8 semaines et coûte 15 000 dollars par module.

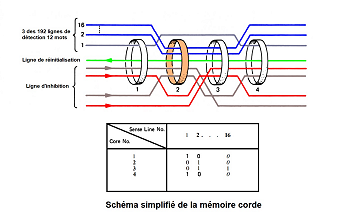

Au début de la production, deux techniciennes, surnommées les "tisseuses de mémoire", s’installent l'une en face de l'autre et tissent à la main une myriade de fils dans de petits noyaux, poussant une aiguille creuse qui contenait la longueur de fil nécessaire, d'un côté à l'autre. Chaque noyau a, potentiellement après tissage, 192 fils de détection (mais, étant donné que le système utilise une parité impaire, au maximum 15 des 16 bits peuvent être élevés. Ainsi, au maximum 180 fils de détection passeraient par un noyau) qui le traversent ou l'entourent (de sorte que chaque noyau stocke 12 mots de données), ainsi que 10 fils supplémentaires : un dit "fixe" pour les retourner à l'état défini, un de réinitialisation et huit d'inhibitions (7 lignes adresse + 1 parité) pour empêcher tout retournement sauf pour le noyau souhaité.

À partir de 1965, une entreprise de Nouvelle-Angleterre, la United Shoe Machinery Company, conçoit une machine permettant de partiellement automatiser le processus. Elle combine le positionnement automatique des noyaux et l’enfilage manuel effectué par les techniciennes de Raytheon. Le système guide l’opératrice pour qu’elle passe rapidement le fil à travers les noyaux, avant que la machine ne repositionne le châssis pour le filage suivant. Néanmoins, le processus reste extrêmement lent, et un programme peut prendre plusieurs semaines, voire plusieurs mois, en incluant le temps nécessaire pour les tests. Toute erreur dans le tissage implique de recommencer le module en entier.

Pour ce faire, le code natif de l'AGC est converti à l’aide d'un assembleur appelé YUL (voir description détaillée), afin de produire une bande perforée en Mylar. Un système automatisé lit cette bande et, pas à pas, déplace le châssis du plan mémoire afin de positionner les noyaux appropriés pour l'opération de tissage. La machine indexe l'emplacement particulier d'un noyau, puis la technicienne passe l'aiguille (aiguille creuse contenant environ 6 m d'un fil fin en alliage de nickel servant de ligne de détection) à travers un guide muni d'un orifice, permettant ainsi au fil de passer par le bon noyau. Lorsque l’aiguille passe à travers l'orifice, elle déclenche un interrupteur, qui fait avancer le lecteur de bande et déplace le plan mémoire, positionnant ainsi un nouveau noyau à tisser. En même temps, le guide s'abaisse, tirant le fil autour de l'une des broches en nylon et l'écartant du centre du noyau nouvellement tissé, afin de préparer l’enfilage suivant (voir vidéo promotionnelle en bas de page). Une fois tous les noyaux tissés et les connexions effectuées, les broches en nylon qui maintiennent temporairement le fil sont retirée. On replie alors délicatement, tout en appuyant sur les fils en place, l'ensemble de l'assemblage, qui forme au final une structure de type sandwich. L'appareillage est ensuite inséré dans un carter de protection. Le module de mémoire à cordes ainsi obtenu est alors testé électriquement par un système automatisé, à nouveau contrôlé par un ruban perforé.

Anecdote : Qui l'aurait cru.. C’est United Shoe Machinery Company, une entreprise de Nouvelle-Angleterre spécialisée dans les machines de fabrication de chaussures, qui met au point la machine capable d’automatiser partiellement le tissage des mémoires à corde pour l’AGC. Ainsi, le travail minutieux et quasi artisanal de ces techniciennes, issues d’une tradition textile bien ancrée dans la région, se marie à une technologie de pointe, illustrant parfaitement comment l’industrie spatiale puise dans des savoir-faire anciens pour réaliser des exploits technologiques sans précédent. |

La mémoire fixe de l'AGC est configurée comme suit : L'AGC contient six modules de mémoire à corde. Les 512 cœurs de chaque module sont disposés physiquement en deux couches de 256 cœurs (mais électriquement en quatre plans de 128 cœurs). Une ligne de détection et de réinitialisation traverse tous les cœurs d'un plan, permettant de sélectionner un plan particulier dans le module. Chaque noyau a des lignes de détection pour 12 mots de données de 16 bits chacun (15 bits + un de parité). Un groupe de 16 lignes de détection est appelé un brin, et il y a 12 brins par module. Il faut savoir que les cœurs n'occupent qu'environ la moitié de l'espace d'un module. Autour des noyaux se trouvent des centaines de résistances et de diodes qui sont utilisées pour sélectionner le mot souhaité. Ces composants sont montés avec la technique fagotage (Corwood), les composants étant installés verticalement à travers des trous dans le module.

Le saviez vous ? Les cœurs (ou noyaux) utilisés dans la mémoire à corde (ROM) sont plutôt gros : 6,32 mm de diamètre (0,249 in), environ 3 fois le diamètre de ceux utilisés dans la mémoire vive (voir ci-dessous). Ainsi, il ne faut que 3072 cœurs pour y stocker les 36K de mots, tandis qu'il faut 32 768 noyaux de ferrite au lithium (environ 1,2 mm de rayon) fabriqués par EMI ou RCA pour contenir les 2K de données de la RAM (1 noyau égal 1 bit). Les noyaux de la mémoire à corde ne sont pas des noyaux de ferrite ordinaires, mais un ruban de mo-perm pour Molybdène Permalloy (alliage de 81 % de nickel avec 17 % de fer et 2 % de molybdène ou NiFe17Mo2) de 0,0031 mm (0,000125 in) d'épaisseur, enroulé autour d'une bobine en acier. Ce matériau magnétique légèrement plus souple réduit la force magnétique nécessaire pour inverser la polarité du grand noyau. En outre, l'extrême finesse du ruban réduit les courants de Foucault à l'intérieur du noyau, ce qui accélère la commutation. La mémoire à corde atteint une densité de 1500 bits pour chaque pouce cube (1 in³ égal 16,38 cm³), y compris toute l'électronique de commande et de détection, les interconnexions et le matériel d'emballage. Cette densité est environ 5 fois supérieure à celle de la mémoire centrale effaçable.

Lorsqu'une mémoire à corde est tissée avec précaution, avec environ 800 mètres de fil, les données sont stockées de façon permanente à l'intérieur. Le résultat donne une mémoire indestructible, sauf si le module est détruit physiquement ou en cas de défaillance d'une ou plusieurs diodes semi-conductrices. Elle ne peut pas être effacée, modifiée ou corrompue. L'inconvénient est que sa production est très difficile à réaliser et encore plus difficile à corriger lorsqu'une erreur est trouvée. Cependant, c'est aussi un avantage car cela signifie que les "bonnes idées" de dernière minute peuvent être ignorées. Le logiciel Apollo n'est pas écrit sur des disques durs ou de la mémoire flash. C'est quelque chose de réel, de physique que vous pouvez littéralement tenir dans vos mains.

Comparatif de la taille des différents noyaux/cœur. Le premier et le second sont utilisés respectivement dans la mémoire à corde et dans la RAM (capture d'écran vidéo CuriousMarc sur YouTube) |

COMMENT FONCTIONNE-T-ELLE ??

L'AGC étant une machine 16 bits, sa mémoire morte stocke des données dans des mots composés de 15 bits de données (ces 15 bits fournissent une précision suffisante pour atterrir sur la Lune en utilisant des valeurs de double et triple précision au besoin) et d'un bit de parité. Le code d'instruction inclut des sous-programmes pour des opérations doubles et triples. Le temps de cycle de mémoire est de 11,72 µs (microsecondes), soit 85 324 Hz. Cette mémoire stocke de manière permanente sous forme de valeurs fixes la plupart des données critiques telles que des programmes d'application, les constantes de navigation ou la position des étoiles. Elle est relativement peu affectée par les impulsions électromagnétiques et les rayonnements radioactifs.

LA LONGUEUR DES MOTS Comme nous l'avons vu, l'ordinateur est une machine à stockage commun. Cela signifie que les instructions peuvent être exécutées à partir de sa mémoire effaçable ou de sa mémoire fixe, et que les données (évidemment des constantes, dans le cas d'une mémoire fixe) peuvent être stockées dans l'une ou l'autre mémoire. Les tailles de mots des deux types de mémoire doivent être compatibles d'une manière ou d'une autre. La solution la plus simple consiste à créer des mots de longueur égale de 16 bits. L'AGC est quelque peu unique en raison de sa longueur de mot très courte, et les raisons de ce choix sont intéressantes. Une des décision qui devait être prise le plus tôt possible dans la phase de conception était celle de la longueur des mots : plus importante, elle permettrait de traiter des unités de données plus grandes (ou plus précises) en une seule étape et d'accéder directement à un plus grand nombre d'emplacements de mémoire. Mais le matériel serait également plus volumineux. La taille ayant été un facteur décisif dans le développement de l'AGC, la décision a été prise en faveur d'une mémoire effaçable relativement petite, mais d'une mémoire en lecture seule plus importante et d'une longueur de mot relativement faible. La longueur de mot choisie était finalement de 16 bits (14 bits de données, 1 bit de signe, 1 bit de parité). Ce choix-là a été judicieux. De nombreux ordinateurs scientifiques de l'époque utilisaient des mots de 24 bits ou plus et, en général, plus le mot était long, meilleure était la précision des calculs. Le MIT a pris en compte les facteurs suivants pour déterminer la longueur du mot : a) la précision souhaitée pour les variables de navigation, b) la plage des variables d'entrée, c) le format du mot d'instruction. Si un mot qui n'est pas une puissance de deux peut sembler bizarre aujourd'hui, les ordinateurs des années 1960 étaient conçus avec une taille de mot adaptée au problème. |

La mémoire fixe de l'ordinateur est de type transformateur et a été développée au MIT/IL. Une propriété de décodage d'adresse est incorporée dans sa structure de câblage. En raison de ce décodage d'adresse interne, le temps de cycle n'est pas aussi court que celui de certaines autres mémoires à transformateur dont le décodage d'adresse est externe. La densité de bits qui en résulte est extrêmement élevée : environ 1500 bits par 16,38 cm3(1 in3), y compris toute l'électronique de commande et de détection, les interconnexions et le matériel de conditionnement. Cette haute densité de stockage est obtenue en stockant un grand nombre de bits dans chaque noyau magnétique. Ce schéma de mémoire est incroyablement économe en espace, car les cœurs peuvent être utilisés par (jusqu'à) 192 fils, ce qui donne une masse dense de fils en boucle.

Cette technologie est en fait différente de la mémoire effaçable. D'une part, elle n'utilise PAS de petits noyaux de ferrite et ne dépend donc pas non plus de noyaux qui conservent l'état du bit stocké : elle résulte de la disposition des fils à travers ou à côté des cœurs (noyaux toroïdaux). Si le fil passe dans le noyau, cette section de fil représente un 1 logique, et si le fil contourne le noyau, cette section de fil représente un 0 logique.

Exemple : pour stocker le mot de données 1001000100001111 dans un noyau, les premier, quatrième, huitième et treizième au seizième fils passent par ce noyau, les autres le contournent.

La figure ci-dessous est un schéma simplifié du câblage des noyaux indiquant le décodage des adresses (lignes d'inhibition) et le câblage des lignes de détection. Le nombre total de bits est le nombre de noyaux multiplié par le nombre total de lignes de détection. La mémoire est composée de six modules. Chaque module contient 512 cœurs et 192 lignes de détection et contient donc 192 x 512, soit 98 304 bits d'information. Comme ces informations sont câblées de façon permanente lors de la fabrication, la mémoire est indestructible, sauf en cas de destruction physique ou de défaillance d'une ou plusieurs diodes semi-conductrices dont les fonctions sont décrites ci-dessous. La ROM possède une capacité totale de 36 864 mots qui se décompose ainsi : 6 modules × 512 cœurs/noyaux par module × 192 bits par cœur ÷ 16 bits (15 +1) par mot = 36 864 (36K) mots (soit 72 kilobyte en unité moderne).

Le moyen par lequel un noyau unique dans un module de 512 noyaux est amené à commuter (adressé) est une extension de celui illustré sur la figure ci-dessus. On applique un courant de commutation qui tente d'activer 128 noyaux (ligne de réglage/réinitialisation). Quatre lignes de courant de ce type desservent un module de 512 cœurs. Des courants d'inhibition sont appliqués simultanément à la première ou à la seconde moitié de chaque groupe de 128 cœurs. Deux lignes d'inhibition sont prévues à cet effet. Un autre courant d'inhibition est appliqué à la première ou à la deuxième moitié de chaque demi-groupe. Deux autres lignes d'inhibition sont prévues à cet effet. Six autres paires de lignes d'inhibition existent dans le but de réduire successivement de moitié les groupes de noyaux non inhibés, jusqu'à ce qu'il n'y ait plus qu'un seul noyau non inhibé. Un élément de chaque paire d'inhibiteurs transporte le courant à la fois.

Il y a huit paires en tout pour sélectionner entre 27 cœurs, dont sept paires correspondent aux sept bits d'adresse de poids faible. La huitième paire est logiquement redondante, étant sélectionnée par la parité de l'adresse. La redondance est utilisée pour réduire la quantité de courant nécessaire dans chaque ligne d'inhibition. Une fois que le noyau sélectionné a commuté et que les courants d'inhibition sont supprimés, un courant de réinitialisation est passé à travers tous les noyaux. Seul le noyau qui vient d'être activé change d'état, et les amplificateurs de détection peuvent être activés pendant la partie d'activation ou de réinitialisation du cycle pour lire les informations de la mémoire. Le niveau de bruit pendant la réinitialisation est plus faible que pendant l'activation pour un certain nombre de raisons, mais le temps d'accès (le temps qu'il faut pour lire la mémoire après que l'adresse soit disponible) est plus long. Les deux méthodes ont été utilisées. La conception de l'AGC Bloc II utilise le temps d'accès le plus long et doit par conséquent produire l'adresse plus tôt.

Lors du fonctionnement de la mémoire à corde, un seul noyau est commuté, induisant ainsi une tension dans chaque ligne de détection qui traverse le noyau. Un seul mot est lu à la fois, de sorte que sur les 192 lignes de détection, seules 16 sont connectées aux amplificateurs de détection pour détecter qu'elles ont une tension et donc stocker les mots. Chaque noyau stocke 12 mots, et à l'intérieur de chaque module, un réseau de commutation est inclus afin de ne pas transmettre plus d'un des 12 mots aux bornes de sortie du module. Le principe du réseau de commutation est illustré ci-dessous. Il est constitué de diodes et de résistances connectées de manière à bloquer la sortie de la ligne de détection lorsque les diodes de la ligne de détection sont polarisées en sens inverse, comme dans le cas de d5 et d6 ; et de le transmettre lorsque les diodes des lignes de détection sont polarisées dans le sens direct, comme dans le cas de d1 et d2. Un commutateur de deuxième étage composé de d3 et d4 est utilisé pour sélectionner l'une des six sorties du module à transmettre aux amplificateurs de détection. Seule la ligne sélectionnée dans le module sélectionné est transmise. Toutes les autres sont bloquées par un ou deux jeux de diodes à polarisation inverse. Toutes ces diodes de sélection sont physiquement situées dans les modules "corde" afin de minimiser le nombre de bornes nécessaires pour chaque module. L'application des tensions de sélection aux bornes de sélection de ligne et de module est une partie du décodage d'adresse qui est externe à la corde. L'équilibre est interne.

Anecdote : Le stockage secondaire n'était pas une option : les unités de disque, alors de la taille d'une machine à laver, ne pouvaient même pas tenir dans le vaisseau spatial. Le stockage sur bande magnétique, bien qu'il s'agisse d'une option fiable et viable, a été considéré bien trop tard dans le cycle de développement pour être inclus dans une quelconque conception. |

LES CIRCUITS INTÉGRÉS de l'AGC

L’ordinateur de guidage Apollo est l’un des tout premiers ordinateurs à utiliser des circuits intégrés. Les progrès de cette technologie ont conduit à l’adoption, pour l’AGC Block II, d’une nouvelle porte NOR à trois entrées utilisant une logique RTL (Resistor-Transistor Logic) à faible consommation. Bien que cette logique soit plus simple et plus économique que celle du Block I, elle reste fondée sur une structure élémentaire à base de transistors et de résistances. Ce circuit dissipe moins de la moitié de la puissance de la porte du Block I. De plus, deux de ces portes ont été fabriquées sur une seule puce de silicium et montées dans un conteneur "flatpack" de 10 broches. Cela a permis de doubler la densité d'emballage par rapport à l'approche Block I. La réduction de puissance a été obtenue dans ces unités logiques en augmentant l'impédance de sortie, ce qui a entraîné une sensibilité accrue du temps de montée aux capacités parasites du câblage. Deux mesures ont été prises pour permettre l'utilisation du nouveau dispositif et réaliser une économie d'énergie : premièrement, des cartes gravées multicouches ont été adoptées comme moyen d'interconnexion à l'intérieur des modules à la place des matrices à ruban soudé, ce qui a réduit la capacité parasite, et deuxièmement, le circuit de synchronisation de l'horloge a été amélioré pour tenir compte de plus grandes incertitudes dans les délais de propagation des signaux.

Les puces de l'AGC sont néanmoins très limitées, elles ne contiennent que six transistors et huit résistances, mettant en œuvre deux portes NOR (NO/OR ou en français : NON-OU) à 3 entrées utilisant une logique résistance-transistor (RTL). Ces circuits intégrés sont coûteux : de 20 à 30 $ chacun (environ 150 en dollars actuels). Malgré cela, ceux-ci permettent d'améliorer la densité par rapport à la logique à transistors de base prévue, rendant ainsi l'AGC possible. La décision d'utiliser des circuits intégrés dans l'AGC est prise en 1962, soit quatre ans seulement après leur invention. Cette décision est critique pour le succès de l'AGC et un moment clé dans l'histoire de l'informatique. À l'époque où l'on décide d'utiliser des circuits intégrés, la porte NOR est le seul dispositif disponible en grande quantité. La simplicité du circuit permet à plusieurs fabricants de produire des dispositifs interchangeables, de sorte qu'une concurrence raisonnable soit assurée. Grâce au développement récent des process dans les circuits intégrés, la porte NOR peut rester compétitive en termes de vitesse, de puissance et d'immunité au bruit.

Le saviez-vous ? le choix délibéré a été fait d'utiliser un seul type de circuit logique intégré : la porte NOR à trois entrées.. Bien qu'une plus grande variété aurait pu réduire considérablement le nombre de dispositifs par ordinateur, le fait de se consacrer à la fabrication et au contrôle de la qualité d'un seul type de circuit a permis d'obtenir des gains importants en termes de fiabilité.

Le symbole d'une porte NOR est illustré sur le photomontage ci-dessous. C'est une porte logique très simple : si toutes les entrées sont négatives, la sortie est positive. Il peut être surprenant que les portes NOR soient suffisantes pour construire un ordinateur, mais "NOR" est une porte universelle : vous pouvez créer n'importe quelle autre porte logique à partir de portes NOR. Par exemple, en reliant les entrées d'une porte NOR ensemble, on obtient un inverseur (ou porte "NON"). En plaçant un inverseur sur la sortie d'une porte NOR, on obtient une porte "OU". Le fait de placer des inverseurs sur les entrées d'une porte NOR produit une porte "ET". Des circuits plus complexes, tels que des bascules, des additionneurs et des compteurs, peuvent être construits à partir de ces portes.

En fonctionnement normal, le circuit est alimenté sous 3,3 V et consomme environ 15 mW, mais il est qualifié pour fonctionner jusqu'à 8 V et dissiper jusqu'à 100 mW. La température nominale sans alimentation est de 150°C. La simplicité de base de la porte à trois entrées facilite un processus de sélection efficace. Tous les transistors et résistances peuvent être testés pour assurer l'uniformité du produit. La simplicité du circuit permet également de détecter et de diagnostiquer rapidement les défaillances insidieuses sans avoir à recourir à des tests approfondis comme c'est le cas avec des circuits plus complexes. Un autre circuit intégré (l'amplificateur de sens, possédant six transistors et neuf résistances) est utilisé dans les circuits de mémoire de l'ordinateur de guidage d'Apollo.

L'AGC Block II utilise 2 826 circuits intégrés. Un total de 120 se situent dans les modules logiques, soit 240 portes par module.

Anecdote : Dans le livre "The Innovators : How a Group of Inventors, Hackers, Geniuses and Geeks Created the Digital Revolution" (2014), l'auteur Walter Isaacson observe que les 75 AGC qui ont été construits ont fini par contenir 5000 micropuces, toutes identiques, et que c'est la compagnie Fairchild qui a décroché le contrat pour les fournir. En juillet 1969, lorsque Neil Armstrong pose le pied sur la Lune, le programme Apollo avait acheté plus d'un million de micropuces, soit 60% de ce que l’industrie américaine pouvait produire à cette époque.

Ces demandes massives et prévisibles de la part du gouvernement pour le programme Apollo et ses autres projets, ont entraîné une chute rapide du prix de chaque puce. Le premier prototype de puce de lAGC a coûté 1000 $. Au moment de leur mise en production régulière, chacune ne coûtait plus que 20 $.

Pour comparaison, le prix moyen de chaque micropuce du missile Minuteman était de 50 $ en 1962 ; en 1968, il n'était plus que de 2 $.

C'est ainsi qu'a été lancé le marché de la mise en place de micropuces dans des dispositifs destinés à la grande consommation. Les premiers appareils grand public à utiliser des puces sont des appareils auditifs, car ils se doivent d'être très petits et se vendent même s'ils sont assez chers.

FONCTIONNEMENT DE L'AGC

Le processeur central effectue toutes les opérations arithmétiques nécessaires de l'ordinateur, met en mémoire tampon toutes les données provenant et y allant, vérifie la parité correcte de tous les mots provenant de la mémoire et génère un bit de parité pour tous les mots écrits en mémoire. Il se compose de registres à bascule, de la logique d'écriture, d'effacement et de contrôle, d'amplificateurs d'écriture, d'un registre tampon mémoire, d'un registre d'adresse mémoire et d'un décodeur et de la logique de parité.

Tous les registres du CPU sont mappés en mémoire. Les registres aux adresses 00-23 (octal) sont au cœur des opérations CPU, du point de vue du jeu d'instructions. Les registres des adresses 00 à 07 sont des bascules (enfin, sauf pour 07) internes au processeur ; tous les autres registres sont des emplacements de mémoire effaçables spécialement gérés. Chaque fois que ces registres de bascule sont accédés, leur contenu est copié dans leurs emplacements de mémoire effaçables correspondants. Ce lien est à sens unique ; les emplacements de mémoire effaçables 00-07 ne peuvent jamais être lus, car toutes les tentatives de le faire seront redirigées vers les bascules correspondantes. |

Principalement, le processeur central exécute les opérations indiquées par les instructions de base du programme stockées en mémoire. La communication à l'intérieur du processeur central est réalisée par l'intermédiaire des amplificateurs d'écriture. Les données circulent de la mémoire vers les registres à bascule (ou vice versa), entre les différents registres à bascule individuels ou dans le processeur central à partir de sources externes. Dans tous les cas, les données sont placées sur les lignes d'écriture et acheminées vers un registre spécifique ou vers une autre zone fonctionnelle sous le contrôle de la logique d'écriture, d'effacement et de lecture. La section logique accepte les impulsions de commande du générateur de séquence et génère des signaux pour lire le contenu d'un registre sur les lignes d'écriture et écrire ce contenu dans un autre registre du processeur central ou dans une autre zone fonctionnelle de l'ordinateur. L'emplacement particulier de la mémoire est spécifié par le contenu du registre d'adresse mémoire. L'adresse est introduite à partir des lignes "d'écriture" dans ce registre, dont la sortie est décodée par la logique du décodeur d'adresse. Les données sont ensuite transférées de la mémoire vers le registre tampon de mémoire.

Fun fact : quand je parle du CPU de l'AGC, je tiens à souligner qu'il n'y a aucune puce de microprocesseur impliquée. Le CPU est construit à partir de milliers de porte NOR individuelles (il en est le plus gros consommateur). Le processeur central se compose de plusieurs registres (lire ci-dessous), de l'additionneur, des amplificateurs d'écriture (WA pour Write Amplifiers) et du bloc de parité. Tous ses registres sont des registres à bascule (5) à porte NOR qui peuvent être lus de manière non destructive.

L'AGC dispose d'un petit ensemble de registres pour stocker temporairement des valeurs en dehors de la mémoire centrale. Il utilise peu de registres à bascule pour des raisons de taille et de masse, néanmoins sept registres clés de l'ordinateur en utilisent :

- l'accumulateur central, registre 00000, La plupart des instructions font référence à A.

- l'accumulateur inférieur, 000001, "L" utilisé dans la multiplication, la division et toutes les opérations de double précision.

- registre d'adresse de retour, 000002, "Q".

- banque de registre effaçable, 000003, "EB", bits 9, 10, 11.

- banque de registre fixe, 000004, "FB", bits 11, 12, 13, 14, 15.

- compteur de programme, 000005, "Z", contient L+1, où L est l'adresse de l'instruction en cours.

- registre des deux banques, 000006, "BB" (les données stockées dans EB et FB sont automatiquement regroupées ici), effaçable : bits 1, 2, 3. Fixe : bits 11, 12, 13, 14, 15.

L'utilisation de banques de registres permet d'adresser toute la mémoire de la machine. Le plus grand nombre qui peut être contenu dans 12 bits est 8 192. La mémoire fixe de l'ordinateur Apollo contient plus de quatre fois ce nombre d'emplacements. Par conséquent, la mémoire est divisée en "banques" de noyaux, et l'adressage peut être géré en indiquant d'abord quelle banque et ensuite quelle adresse à l'intérieur de la banque. Par exemple, si l'on prend la métaphore "adresse" au pied de la lettre, il y a probablement des dizaines d'adresses "110 rue Jules Verne" dans n'importe quel département, mais en indiquant la ville appropriée sur une enveloppe, une lettre peut être livrée sans difficulté à l'adresse 110 rue Jules Verne visée.

Les banques informatiques sont comme les villes de l'analogie. Le registre de la banque effaçable ne contient que 3 bits qui servent à étendre l'adressage direct de la mémoire effaçable à sa région "supérieure", et le registre de la banque fixe contient 5 bits pour indiquer quelle banque de mémoire corde adresser.